Přichází doba třínanometrová?

Věčný souboj výrobců čipů o nejpokročilejší výrobní technologii pokračuje. Po nástupu 7- a 5nm procesů je aktuálně na řadě další krok: posun k hranici tří nanometrů.

Věčný souboj výrobců čipů o nejpokročilejší výrobní technologii pokračuje. Po nástupu 7- a 5nm procesů je aktuálně na řadě další krok: posun k hranici tří nanometrů.

Ačkoli miniaturizaci v tomto řádu by si před lety asi stěží dokázal někdo představit, je už realitou a první výrobci se chystají přejít na tento výrobní proces, který by měl pomoci stvořit ještě výkonnější a menší čipy s nižší spotřebou. Lídry v této oblasti jsou dva asijští rivalové – Samsung a TSMC.

Samsung: Sázka na nové řešení

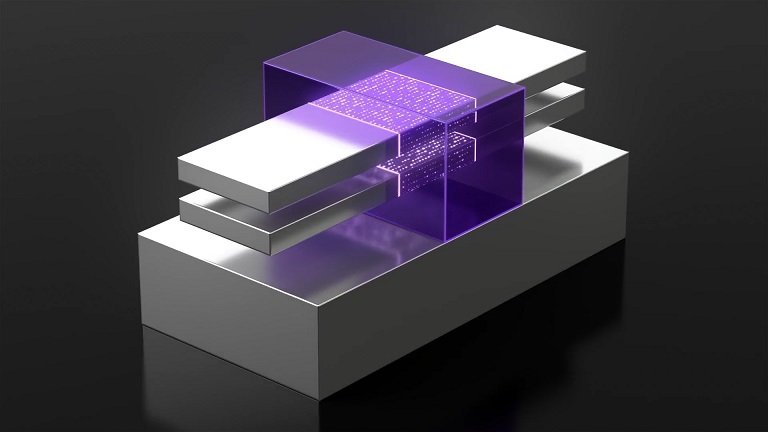

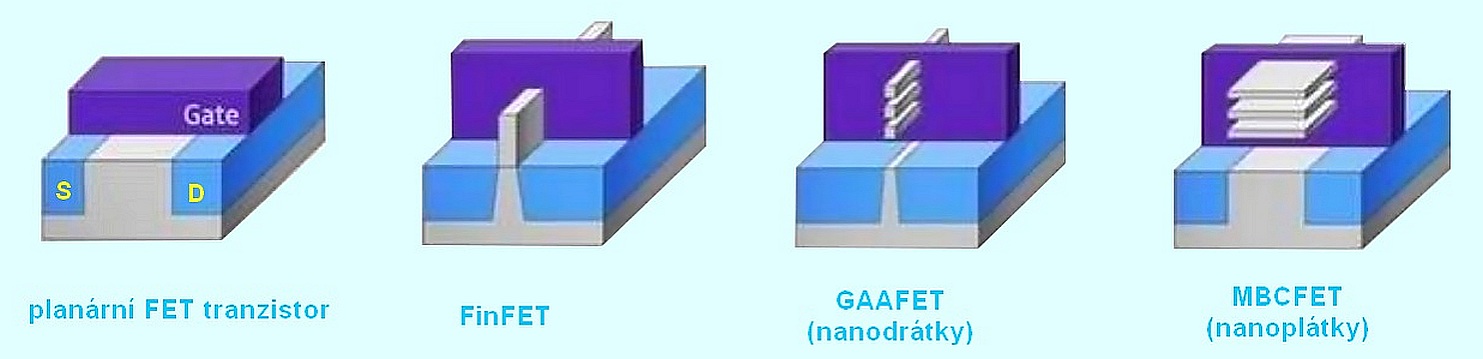

Samsung už loni představil vlastní 3nm výrobní proces 3GAE, vůbec první technologii s 3D tranzistory s inovativní architekturou MBCFET (Multi-Bridge-Channel FET), vytvořenou na základě nové struktury tranzistorů GAA (Gate-All-Around) pomocí nanočipových zařízení. Tato technologie na bázi nanovláken, která nahrazuje technologii tranzistorů předchozí generace FinFET, by měla významně zvýšit jejich výkon a také být kompatibilní se stávajícími technologiemi a zařízeními FinFET výrobního procesu. Výrobce má 3nm proces rozdělen na 3GAE a 3GAP (přičemž druhý z nich má nabídnout lepší výkon).

Na loňské konferenci SFF v Japonsku firma uvedla, že ve srovnání se současným 7nm procesem může 3nm řešení zredukovat plochu jádra o 45 %, spotřebu energie o polovinu a výkon zlepšit o 35 %. Vytvořila už i funkční testovací čipy. Do sériové výroby by se novinka přes zdržení způsobené koronavirovou pandemií mohla dostat už koncem roku 2021.

Pro úspěch bude však důležitá nejen cena, ale i výtěžnost (tzn. procento bezchybných čipů na waferu), s níž měla firma problémy při nasazení 7nm procesu s využitím pokročilejší, ale ještě nepříliš zavedené výrobní technologie EUV (extrémní UV litografie využívající ultrakrátké vlnové délky), zatímco ostatní výrobci se vesměs zatím drží starší a praxí prověřené optické litografie.

TSMC: Vylepšit již osvědčené

Svůj 3nm proces nedávno odhalila i tchajwanská TSMC s tím, že by se čipy vyráběné s využitím této technologie v nově budované továrně, do níž investovala 20 mil. dolarů, mohly na trhu objevit v předprodukční ověřovací sérii už příští rok a sériová výroba začít koncem roku 2022.

Výrobce zůstal u architektury FinFET, kterou se mu podařilo pro 3nm technologii vylepšit na dostatečně vysoký výkon, aby nebylo nutné provést změnu 3D struktury tranzistorů. Na rozdíl od konkurence nepoužije nový typ tranzistorů, jako jsou nanodrátky/nanodestičky (tzv. GAAFET), přitom má přinést stejné zlepšení jako 5nm výroba, kterou TSMC již odstartovala letos s označením N5.

S detaily o 3nm výrobním procesu zatím firma šetří, ale podle expertů je vysoce pravděpodobné, že bude používat jak litografická zařízení pro hluboké ultrafialové záření (DUV), tak extrémní ultrafialové záření (EUV), bez něhož by asi výroba pracující s tak ultraminiaturními prvky nebyla ani možná. Vzhledem k tomu, že předchozí systém N5 používá až 14 vrstev EUV, bude počet vrstev použitý v N3 ještě vyšší.

Stále menší a výkonnější

Na rozdíl od prvních planárních (plochých) tranzistorů jsou výkonové parametry následujících generací i jejich konstrukce neustále vylepšovány pomocí nových řešení využívajících 3D architekturu. Mezi poslední patří FinFET (Fin Field-Effect Transistor), tzn. polem řízený tranzistor s žebry, kde je vodivý kanál mezi elektrodami tvořen tenkým žebrem (fin) obaleným hradlem (gate – G), a GAA (Gate All Around), kdy hradlo obepíná celý kanál ze všech stran pro maximální výkon a efektivitu využití prostoru.